PKG이 중요해지는 이유: ①기능은 모아야 하고, 칩 크기는 작아져야 하고

PKG이 중요해지는 이유: ②공정 개선은 힘들고, 효율은 떨어지고

과거에는 게이트의 길이 축소, 쉽게 말해 미세화 공정의 진행속도가 0.7배씩 줄어드는 노드의 진행 과정보다 더 빨랐습니다.그러나 20nm대에 접어들면서 이런 트렌드는 바뀌게 됩니다.예를 들어, 업체에서는 7nm라 주장하지만 사실 게이트의 길이를 재보면 10nm 정도라는 거죠. 미세공정화가 진행될수록 실질적인 게이트 길이 축소가 더욱 힘들어졌기 때문입니다.

하지만 아래 그림에서 보실 수 있듯, 게이트 길이 축소에 따른성능 개선폭은 크게 나아지지 않고 있죠. 그러나 가장 오른쪽그림에서 보실 수 있듯이, 후공정의 변화에 따른 성능 개선폭은매우 큽니다. 최근 후공정은 과거와는 달리 전공정만큼이나 그중요도가 높아지고 있습니다.

차세대 Packing은 결국 적층 기술, 무어의 법칙을 새로 쓰다

발상의 전환과 3D Stacked IC의 개념 도입

• 3D Stacked IC는 말 그대로 Chip을 수직으로 쌓아 연결하는 방식 2차원 집적화에 비해 단위 면적당 집적도가 비약적으로 상승

• 미세화 공정의 발전 없이 면적당 집적도를 향상시킬 수 있는 방안이며, 트랜지스터 간 배선 길이도 줄어 칩의 성능 향상이 가능

• 게다가 서로 다른 소자를 수직으로 연결하여 결합할 경우, 새로운 특성 창출 또는 다기능 원칩화(One Chip화)가 가능

적층 기술의 핵심은 Chip의 구조 변화가 아닌, Packaging 기술

• 다양한 시도 중 최근 각광받고 있는 시도는 Chip을 수직으로 쌓는 것 2차원의 집적화에 비해 단위 면적당 집적도 비약적 상승

• Chip을 수직으로 쌓을 시, 단위 면적당 집적도가 상승하고, 트랜지스터 간 배선의 길이가 줄어 들어 칩의 성능 향상이 가능

• 또한 서로 다른 소자를 수직으로 연결하여 결합할 경우, 새로운 특성을 창출하는 것도 가능

차세대 Packaging, TSV(Trough Silicon Via) 기술과 기술적 한계

TSV가 기존 Wire Bonding 방식 대비 갖는 장점은 명확

• TSV는 칩 내부에 Microhole을 수직으로 뚫어 chip-to-chip communication을 가능케 함 와이어를 거칠 필요가 없음

• 와이어가 불필요하므로 Die 공간 활용도 상승하며, 와이어를 거치며 발생하는 지연 시간과 전력 소모 문제가 해결

• 처리 속도의 비약적 향상은 물론, 전력 소모도 크게 줄이며 차세대 메모리 PKG 방식으로 주목

TSV 기술을 개발한다 하더라도 남게 되는 2가지 문제: 1)설계의 어려움과 2)발열 문제

• TSV를 위해서는 중앙에 Microhole을 배치해야 함 IP 설계 시 Microhole 지역을 피해가야 하므로 칩 설계 복잡성이 증가

• SoC의 경우, 중앙에 Microhole을 비워두고 설계할 수 있을 만큼 공간이 충분치 못하기 때문에 원칩화가 어려워짐

• 결정적으로 기본적인 발열 문제가 심한 SoC를 수직 적층 시, 발열 문제의 심각성 배로 증가

기술적, 비용적 한계로 TSV는 메모리에 우선 적용 2.5D의 등장

TSV의 기술적 한계로 완전한 3D Stacked IC 구현에는 실패, 2.5D Stacked IC의 등장

• TSV 이용하여 수직으로 DRAM 칩을 적층하여 만든 HBM을 서버용 High-end GPU와 연결 할 때 인터포저 이용하여 수평 연결

3D와 2D를 합친 방식이라 하여 2.5D Stacked IC의 개념을 도입

• 최종 단계인 완전한 3D Stacked IC를 개발하기 위한 연구 지속

TSV는 기술적인 문제 외에 비용 문제도 심각

• 복잡한 설계로 인한 높은 제조 기술 난이도와 비용 실리콘 다이에 일정한 관통 구멍을 형성하고 구리를 박는 비용이 상당

• 관통 전극 주변에는 전극과 실리콘 사이에서 발생하는 저항을 막기 위해 필연적으로 데드 스페이스가 발생 다이 면적 증가

• TSV 적용해 제조한 HBM은 일반적인 칩 대비 높은 비용과 낮은 수율로 인해 높은 판매가 형성(일반 제품 대비 2배 이상)

삼성이 TSMC 대비 상대적으로 가장 뒤쳐지는 부분은 PKG Solution: 적극 투자 예상

Package Solution 부문은 여전히 취약 High-end Foundry에서 Total Solution 측면의 경쟁력 강화 필요

삼성전기 FOPLP 부문 인수 후 처음 발표된 SFF USA 2019에서 양산 진행 중이라는 것을 강조

경쟁사 대비 취약했던 PKG 부문에서 개선되고 있음을 강력하게 시사

2.5D I-Cube, 3D SiP 등 향후에 반도체 경쟁력 극대화를 위해서는 TSMC와 같은 직접적 개발 및 관리가 필요

2.5D 실리콘 인터포저(CoS) 사용한 대형 PKG, 2.5D I-Cube with HBM2, 30um에서의 3D SiP, 10nm 3D SiP(D2W) 등의 PKG 공개

Total Solution 측면 고려시, 삼성전자는 메모리와 시스템 반도체의 시너지 극대화를 위한 패키징 투자 강화될 것

투자의 결실을 맺은 삼성전자, 3차원 적층의 시대를 열다

삼성전자는 EUV 공정 적용한 시스템 반도체용 3D 패키징 기술을 개발

• 삼성전자는 최근 3차원 적층 패키지 기술 ‘X-Cube’를 발표, 해당 기술로 7nm EUV 공정 적용된 칩을 수직 적층한 테스트 칩 생산

• X-Cube 기술은 Logic과 SRAM을 단독으로 설계 및 생산한 뒤, 자사 TSV 기술 활용하여 칩을 위로 쌓아 올리는 방식으로 구현

• 평면으로 다이(die)를 배열할 떄보다 반도체 크기를 줄이고, 전력 효율 향상까지 모색할 수 있는 차세대 패키징 기술

삼성전자는 Front-end 뿐 아니라, Back-end에서도 TSMC와의 경쟁을 지속

• TSMC는 후공정 패키징 분야에서 3차원 적층 기술인 SoIC(System on IC) 개발에 상당한 성과를 거두고 상용화 막바지 단계 진입

• 현재 ’21년 5nm 공정에 적용하여 양산을 시작하는 것이 목표이며, 설계 자동화 업체들은 관련 개발 도구 출시 앞둔 것으로 파악

• 특히 디지타임스는 TSMC의 SoIC가 “회로 선폭을 4.5~6㎛로 줄인 것이 삼성전자의 적층기술(X-Cube)과 차별된다"고 전함

OSAT 시장 전망 및 경쟁구도: Advanced PKG 부문의 성장 기대

Advanced PKG 상용화 시, Back-end 장비에도 주목해야 할 것

TSV와 같은 Advanced PKG 상용화 시, chip-to-chip 연결을 위해 드릴링(Drilling) 과정이 필요

• 얇고, 일정 수준으로 휘어진 칩들을 수직적층 하여 chip-to-chip으로 연결하기 위해서는 드릴링이 필요

• 최근 정밀한 드릴링을 위해 레이저 기술 응용한 레이저 드릴링이 각광을 받고 있는 상황

• 기존에 레이저 마킹, 커팅 등의 사업을 하고 있던 기업이 R&D 통해 어닐링 또는 드릴링 장비 시장에 진입하는 케이스 주목

Back Grinding 관련 업체에 대한 관심도 필요

• Hgih-end PKG을 위해서는 칩을 최대한 얇게 가공하는 것이 핵심 웨이퍼 두께와 칩 패키징은 반비례 관계

• Back Grinding은 High-end PKG 뿐 아니라, 일반적인 MCP 등에서도 매우 중요 향후 적층 단수 상승할수록 중요도 상승할 것

• 연삭 및 연마를 담당하는 기업 뿐 아니라, 라미네이션 공정에서의 소재 등에도 관심을 가질 필요가 있을 것

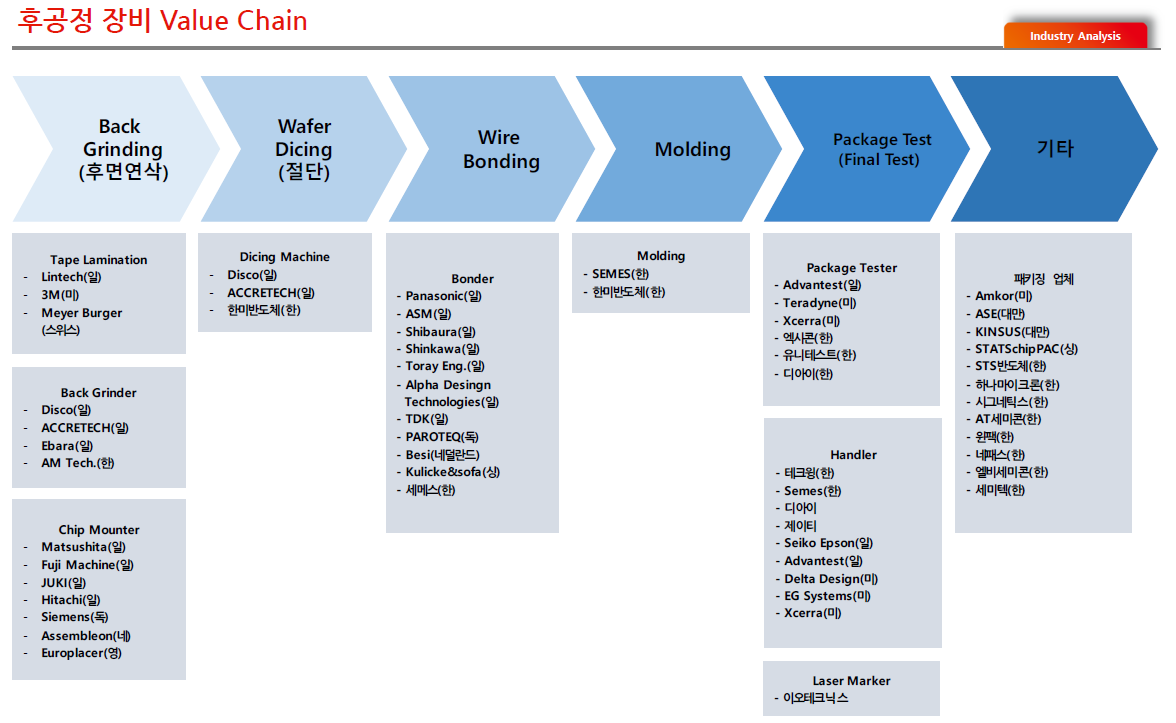

후공정 장비 Value Chain

후공정 소재 Value Chain